Hall Ticket Number:

## Code No. : 15454 H

## VASAVI COLLEGE OF ENGINEERING (AUTONOMOUS), HYDERABAD

Accredited by NAAC with A++ Grade

B.E. (E.C.E. : Honours) V-Semester Main Examinations, Jan./Feb.-2024

## **FPGA Based System Design**

## Time: 3 hours

Max. Marks: 60

Note: Answer all questions from Part-A and any FIVE from Part-B

Part-A  $(10 \times 2 = 20 \text{ Marks})$

| Q. No. | Stem of the question                                                                                                                                                                           | M | L | CO | РО | PSO |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----|----|-----|

| 1.     | How many 1-bit 2x1 muxes are required to construct a 16-bit 8x1 mux?                                                                                                                           | 2 | 1 | 1  | 1  | 1   |

| 2.     | Write a logical expression for a 4-input multiplexer whose inputs are a, b, c, d and select lines are s1 and s0.                                                                               | 2 | 2 | 1  | 1  | 1   |

| 3.     | All bits of an 8-bit number a7a6a5a4a3a2a1a0 are fed to a logic circuit which                                                                                                                  | 2 | 2 | 1  | 2  | 1   |

|        | has an output, <b>plnd</b> . When the 8-bit input is the same as seen in forward and reverse direction, <b>plnd</b> becomes 1. Write the logical expression for                                |   |   |    |    |     |

| 4.     | plnd.<br>Write a simple, but complete Verilog module which causes the output $y$ to<br>become 1, only when all the bits of an 8-bit input $a$ are at logic-1. In all<br>other cases, $y$ is 0. | 2 | 1 | 1  | 1  | 1   |

| 5.     | A sequential circuit has M states. (i) How many flipflops are required in the design if one-hot encoding is used? (ii) How many flipflops are required if binary encoding is used?             | 2 | 2 | 2  | 2  | 1   |

| 6.     | What is the extra logic circuitry in an asynchronous FIFO which is not required in synchronous FIFO?                                                                                           | 2 | 1 | 2  | 1  | 1   |

| 7.     | In the context of IC packages, expand the following acronyms: PGA, BGA, FBGA, QFP.                                                                                                             | 2 | 1 | 4  | 1  | 1   |

| 8.     | What are the main programmable resources in an FPGA?                                                                                                                                           | 2 | 1 | 4  | 1  | 1   |

| 9.     | What are the main types of FPGA, based on programming type?                                                                                                                                    | 2 | 1 | 5  | 1  | 1   |

| 10.    | In the implementation of a logic design on the FPGA (using Vivado), in which step will we get an error if the constraints file is not included?                                                | 2 | 1 | 5  | 1  | 1   |

Contd... 2

:: 2 ::

Code No. : 15454 H

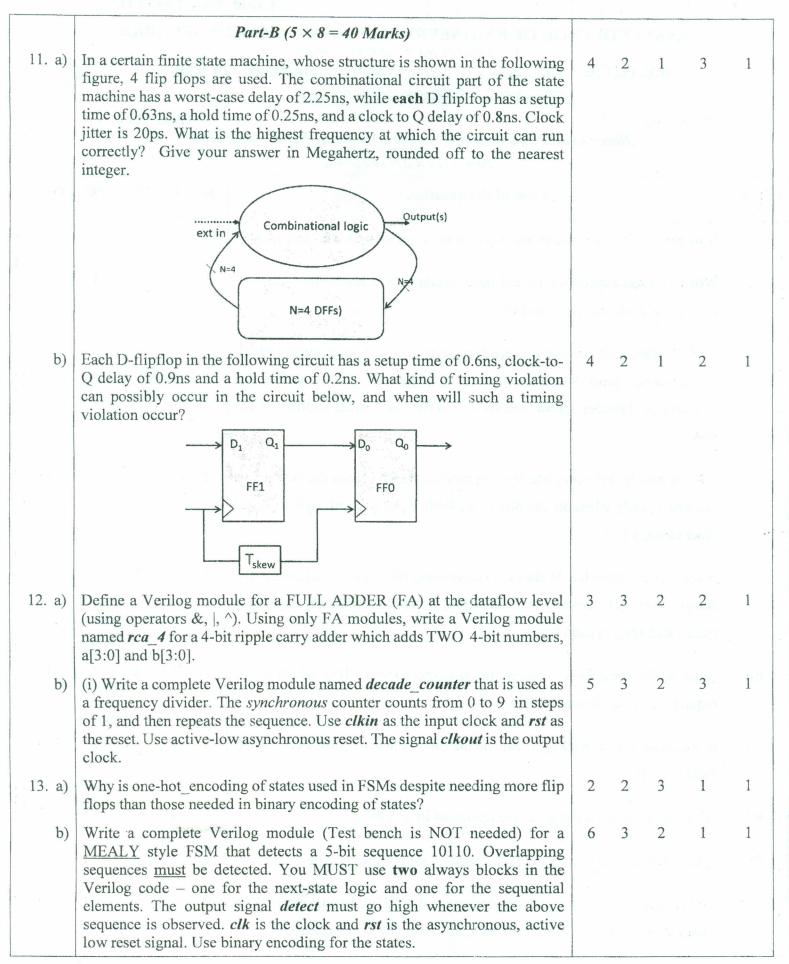

| 14. a) | What are the main functions of an I/O pad in an FPGA?                                                                                                                                                                                                                                                                                                                                 | 3 | 1 | 4 | 2 | 1 |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|

| b)     | Implement the function $F = \sum (1,4,7,8,10,15,18,21,25,28,31)$ using a 5-variable LUT, constructed from 4-variable LUTs.                                                                                                                                                                                                                                                            | 5 | 3 | 4 | 3 | 1 |

| 15. a) | (i) What is the main programmable logic element at the heart of a CLB? (ii) How many logical functions can be implemented from 4 variables?                                                                                                                                                                                                                                           | 4 | 2 | 5 | 1 | 1 |

| b)     | Draw a flow diagram showing the different steps in the generation of a bit file when using the Vivado software. Explain briefly each step.                                                                                                                                                                                                                                            | 4 | 2 | 5 | 2 | 1 |

| 16. a) | An 8-to-3 priority encoder has data inputs in <u>decreasing</u> order of priority as follows: D7, D6, D5, D4, D3, D2, D1, D0. It has a single bit output V which is 1 if any one or more bits are asserted. Write the <u>simplified</u> logic equations for the priority outputs P2, P1, P0 and for the output V.                                                                     | 4 | 3 | 1 | 3 | 1 |

| b)     | Assuming that FULL ADDER / HALF ADDER blocks are available to you, draw a diagram to show how you will add 8 one-bit numbers a, b, c, d, e, f, g, h. Show the connections clearly.                                                                                                                                                                                                    | 4 | 3 | 2 | 2 | 1 |

| 17.    | Answer any <i>two</i> of the following:                                                                                                                                                                                                                                                                                                                                               |   |   |   |   |   |

| a)     | Describe in a few lines, how the fifo_full signal is generated in an <b>asynchronous</b> FIFO.                                                                                                                                                                                                                                                                                        | 4 | 2 | 3 | 1 | 1 |

| b)     | The EDA tool vendor Synopsys supplies to the VLSI world, the ASIC synthesis tool called DC (Design Compiler). (i) Why does Synopsys not provide an FPGA synthesis tool, like Vivado? (ii)What information is present is the 'constraints' file used in the implementation of your logic design on an FPGA?                                                                            | 4 | 2 | 4 | 1 | 1 |

| c)     | An FPGA board from Xilinx has an onboard 100MHz clock and 4 seven-<br>segment LED displays. You are required to design a 2-digit BCD counter<br>that displays the seconds on 2 LED displays. This BCD counter requires a<br>1-Hz clock which is derived from 100MHz. Starting from 100MHz clock,<br>how many flipflops (minimum) are needed for the counter and frequency<br>divider? | 4 | 4 | 5 | 3 | 1 |

|        |                                                                                                                                                                                                                                                                                                                                                                                       |   |   |   |   |   |

| M: Marks; L: | Bloom's Taxonomy Level; | CO; Course Outcome; | PO: Programme Outcome |

|--------------|-------------------------|---------------------|-----------------------|

|--------------|-------------------------|---------------------|-----------------------|

| i)   | Blooms Taxonomy Level – 1     | 20% |

|------|-------------------------------|-----|

| ii)  | Blooms Taxonomy Level – 2     | 40% |

| iii) | Blooms Taxonomy Level – 3 & 4 | 40% |

\*\*\*\*\*